更新时间:2022-09-01 22:13:51

在数字计算机中,大量的离散信息都用二进制码表示。一种n位二进制码可以表示多达2n个不同的编码信息。译码就是将一个n位的输入码转换成一个m位的输出码,并且有n≤m≤2n,以保证每一个有效的输入码都产生唯一的输出码。译码通过译码器(decoder)来完成,译码器是一个组合电路,在它的输入端加载一个n位的二进制码,它就会在输出端产生一个m位的二进制码。译码器输入的某些组合可能没有,故在输出端也就得不到对应的m位码。在所有定义的特殊函数中,译码是最重要的,因为这个函数以及相应的功能模块普遍存在于其他函数和功能模块中。

在这一节,实现译码功能的功能模块称为n输入m输出译码器,简单表示为n-m译码器,其中m≤2n。使用译码器的目的是要从n个输入变量中产生不超过2n个的最小项。假设n=1,m=2,我们就可以得到1-2译码函数,其输入为A,输出为D0和D1,真值表如图3-12a所示。如果A=0,则D0=1,D1=0;如果A=1,则D0=0,D1=1。通过真值表可知,D0=A,D1=A。具体的电路如图3-12b所示。

第二个译码函数n=2且m=4,其真值表如图3-13a所示,它更好地说明了译码器的一般特性。这个表将二变量的最小项作为输出,每一行有一个输出值为1,其余为0。当A1和A0上的两个输入值是数字i的二进制码时,输出Di等于1。从而,此电路可以获得由两个变量组成的4个最小项,每个输出一个。在图3-13b给出的逻辑原理图中,每个最小项通过一个二输入与门来实现,这些与门和两个1-2译码器相连,每个译码器的输出都驱动与门的输入。

对于规模较大的译码器,可以考虑用输入个数更多的与门来一个一个地实现每一个最小项。但糟糕的是,译码器越大,这种方法的门输入成本越高。在这一节,我们介绍使用分级思想和一组与门来构建任意n输入2n输出译码器的设计过程。这样得到的译码器与通过简单增加每个与门的输入个数而得到的译码器相比,门输入成本相等或更少。

为了构造一个3-8译码器(n=3),我们可以采用一个2-4译码器和一个1-2译码器,同时将它们连接到8个二输入与门来形成最小项。采用分层设计,2-4译码器可以由2个1-2译码器连接到4个二输入与门组成,正如我们在图3-13中看到的那样。最终得到的电路如图3-14所示。

一般步骤如下:

1)使k=n。

2)如果k是偶数,则将k除以2得到k/2,并使用2k个与门,这些门被两个译码器驱动,每个译码器有2k/2个输出。如果k是奇数,计算出(k+1)/2和(k-1)/2,并使用2k个与门,这些与门被两个译码器驱动,其中一个译码器有2(k+1)/2个输出,另一个译码器有2(k-1)/2个输出。

3)对于由步骤2)得到的每一个译码器,使用由步骤2)得到的k,重复步骤2),直到k=1。如果k=1,则使用一个1-2译码器。

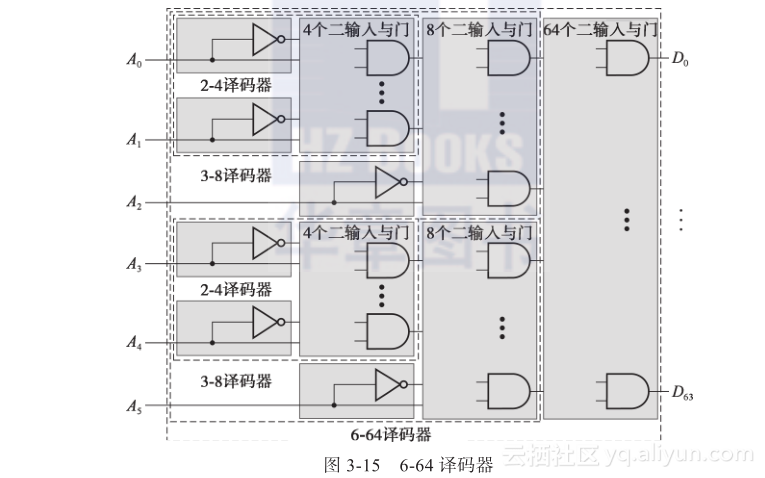

例3-6 6-64译码器

对于一个6-64译码器(k=n=6),在第一次执行完第2)步后,64个二输入与门被两个输出个数为23=8的译码器驱动(即两个3-8译码器)。在第二次执行完第2)步后,k=3。因为k是奇数,则(k+1)/2=2和(k-1)/2=1,8个二输入与门被一个输出个数为22=4的译码器和一个输出个数为21=2的译码器驱动(即一个2-4译码器和一个1-2译码器)。最后,在第三次执行完第2)步后,k=2,4个二输入与门被两个输出个数为2的译码器驱动(即两个1-2译码器)。因为所有的译码器都已被展开,这时可以执行第3)步,算法到此结束。最终的电路结构如图3-15所示,该电路结构的门输入成本为6+2(2×4)+2(2×8)+2×64=182。如果对于每一个最小项使用一个与门,则门输入成本为6+(6×64)=390,所以本方法使门输入成本得以明显减少。

■可能会出现这样的情况:有多个译码器,而且这些译码器有相同的输入变量,这时需要使用另一种扩展方法。在这种情况下,我们并不孤立地实现每一个译码器,而是通过共享来实现几个译码器。例如,假设3个译码器da、db和dc是下列输入变量的函数:

da(A, B, C, D)

db(A, B, C, D)

dc(A, B, C, D)

在da和db之间可以用一个3-8译码器来实现A、B和C的共享;在da和dc之间可以用一个2-4译码器来实现C和D的共享;在db和dc之间可以用一个2-4译码器来实现C和E的共享。如果我们全部实现了这些共享,那么这三个不同的译码器会同时含有变量C,电路就会出现冗余。为了在共享译码器的大小为2时只使用C一次,我们可以考虑如下不同方案:

1)da和db共享(A,B),da和dc共享(C,D)。

2)da和db共享(A,B),db和dc共享(C,E)。

3)da和db共享(A,B,C)。

因为第1)种方案和第2)种方案的开销明显相同,所以我们比较第1)种方案和第3)种方案的开销。对于第1)种方案,函数da、db、dc可减少两个2-4译码器(反相器除外)或者16个门输入。对于第3)种方案,函数da和db可减少一个3-8译码器(反相器除外)或者24个门输入。所以,我们应该采用第3)种方案。将这个过程形式化,并用算法来表示超过了我们目前的学习范畴,这里只是对此方法进行举例说明。

3.5.1 译码器和使能结合

带使能的n-m译码函数,可以通过在译码器的输出端连接m个使能电路来实现。这样,m个相同的使能信号EN与使能电路的使能控制连接。当n=2、m=4时,带使能的2-4译码器及其真值表如图3-16所示。当EN=0时,译码器的所有输出都为0;当EN=1时,译码器的一个输出为1,其他输出都为0,这个为1的输出由(A1,A0)的值来决定。如果这个译码器控制一组灯光的照明,则当EN=0时,所有灯都是熄灭的;而当EN=1时,只有一盏灯是亮的,其他灯都是熄灭的。对于规模大的译码器(n≥4),将使能电路放置在译码器的输入端以及它们的反相端,而不是放在每个译码器的输出端,可以减少门输入成本。

3.7节将介绍采用多路复用器来选择数据。与“选择”相反的操作称为分配(distribu-tion),它可以将来自一条输入线上的信息传送到2n条输出线中的任意一条。执行这种分配任务的电路称为多路分配器(demultiplexer),它由n条选择线的组合控制将输入信号传送到特定的输出端。图3-16所示的带使能的2-4译码器是一个1-4多路分配器的一种实现方式,其中输入EN提供数据,其他输入为选择变量。虽然两个电路有不用的应用,但它们的逻辑图却完全一样。正因为这样,一个带使能输入的译码器又可以称为译码器/多路分配器。输入数据EN与所有4个输出之间都有一条通路,但是输入信息由两条选择线A1和A0控制,只能到达输出中的一个。例如,如果(A1,A0)=10,则加载到输入EN的数据被传送到输出D2,而其他输出仍然是非活动的逻辑0。如果译码器控制4盏灯,(A1,A0)=10且EN在1和0之间做周期性变化,则由D2控制的那盏灯会不断闪烁,其他灯熄灭。

接下来的几个例子说明了使用VHDL和Verilog语言描述译码器的行为,以此作为在第2章首次介绍的每一种语言结构和数据流建模方式的补充。

例3-7 2-4译码器的VHDL模型

图3-17给出了图3-16中2-4译码器电路的VHDL结构描述。该模型使用了基本逻辑门的lcdf_vhdl库,如第2章所述,该库可从本书的配套网站上下载。

图3-18给出了图3-16的2-4译码器电路的VHDL数据流描述。注意,这里的数据流描述要比图3-17的结构描述更简单,而且经常是这样。库、调用与实体声明与图3-16中的那些是完全相同的,因此不再重复说明。

例3-8 2-4译码器的Verilog模型

图3-19给出了图3-16中2-4译码器电路的Verilog结构描述。图3-20给出了这个2-4译码器电路的Verilog数据流描述。这个数据流描述使用了紧跟布尔表达式之后的赋值语句。

■

■3.5.2 基于译码器的组合电路

一个n输入变量的译码器可以产生2n个最小项。因为任何布尔函数都可以由最小项之和表示,所以可以使用一个译码器来产生这些最小项,并由一个额外的或门组合它们来实现最小项之和。按照这种办法,任何n输入m输出的组合电路都可以用1个n―2n译码器和m个或门实现。

通过译码器和或门来实现组合电路的前提是,用最小项之和的形式来表示布尔函数,这可以从真值表或者每个函数的卡诺图中获得。输入变量所有的最小项都可以通过设计或选择一个合适的译码器来产生,再根据每个函数最小项的列表选择相应的最小项作为或门的输入。下面的例子演示了这一过程。

例3-9 用译码器和或门实现1位二进制加法器

在第1章,我们讨论了二进制加法。加法运算中某一位的和输出S与进位输出位C,由该位两个相加的数X和Y以及来自右边(低位)的进位输入Z来产生,如表3-4所示。

从真值表中,我们可以得到该组合电路函数的最小项之和的形式:

S(X, Y, Z)=m(1, 2, 4, 7)

C(X, Y, Z)=m(3, 5, 6, 7)

因为有3个输入和8个最小项,所以我们需要一个3-8译码器。实现过程如图3-21所示,译码器产生输入X、Y和Z的所有8个最小项,产生输出S的或门形成最小项1、2、4和7的逻辑和,产生输出C的或门则形成了最小项3、5、6和7的逻辑和。最小项0没有用到。 ■

一个有许多最小项的函数需要一个多输入的或门。一个有k个最小项的函数可以用另外的2n-k个最小项之和的非来表示。如果函数F最小项的个数超过了F最小项的个数,则函数F的取反形式F可以用更少的最小项表示。在这种情况下,使用或非门比使用或门有优势。或非门的或运算部分可以得到函数F的最小项的逻辑和,或非门的输出泡泡则将该逻辑和取反,给出正常的输出F。

译码器方法可以用来实现任何组合电路。然而,这种实现方法必须和其他可能的方法相比较以便确定***的解决方案。译码器方法也许是***的解决方法,特别是当组合电路有许多输出,而且这些输出都是基于相同的输入,以及每个输出函数可以用少量的最小项来表示的时候。